# CS6303 – COMPUTER ARCHITECTURE

# **LESSION NOTES**

# UNIT I OVERVIEW & INSTRUCTIONS

# **8 GREAT IDEAS**

### 1. Design for Moore's Law

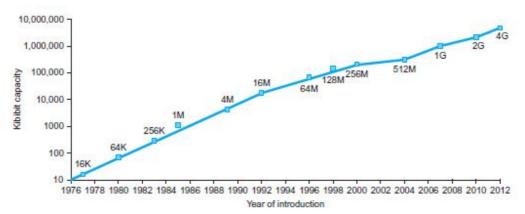

MOORE'S LAW The one constant for computer designers is rapid change, which is driven largely by Moore's Law. It states that integrated circuit resources double every 18–24 months. Moore's Law resulted from a 1965 prediction of such growth in IC capacity made by Gordon Moore, one of the founders of Intel. As computer designs can take years, the resources available per chip can easily double or quadruple between the start and finish of the project. Like a skeet shooter, computer architects must anticipate where the technology will be when the design finishes rather than design for where it starts. We use an "up and to the right" Moore's Law graph to represent designing for rapid change.

### 2. Use Abstraction to Simplify Design

**ABSTRACTION** Both computer architects and programmers had to invent techniques to make themselves more productive, for otherwise design time would lengthen as dramatically as resources grew by Moore's Law. A major productivity technique for hardware and soft ware is to use abstractions to represent the design at different levels of representation; lower-level details are hidden to off er a simpler model at higher levels. We'll use the abstract painting icon to represent this second great idea.

#### 3. Make the common case fast

**COMMON CASE FAST** Making the common case fast will tend to enhance performance better than optimizing the rare case. Ironically, the common case is oft en simpler than the rare case and hence is oft en easier to enhance. This common sense advice implies that you know what the common case is, which is only possible with careful experimentation and measurement. We use a sports car as the icon for making the common case fast, as the most common trip has one or two passengers, and it's surely easier to make a fast sports car than a fast minivan.

#### 4. Performance via parallelism

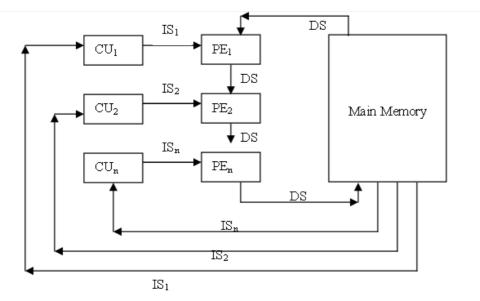

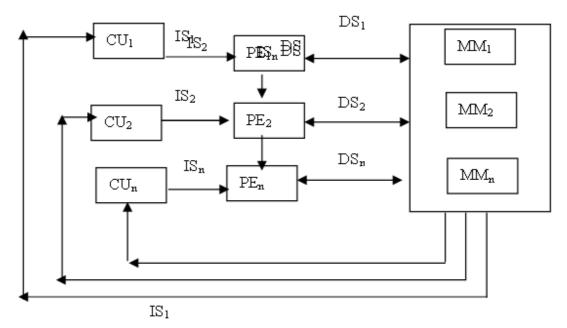

**PARALLELISM** Since the dawn of computing, computer architects have offered designs that get more performance by performing operations in parallel. We'll see many examples of parallelism in this book. We use multiple jet engines of a plane as our icon for parallel performance.

#### 5. Performance via pipelining

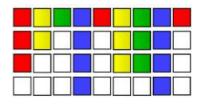

A particular pattern of parallelism is so prevalent in computer architecture that it merits its own name: pipelining. For example, before fire engines, a "bucket brigade" would respond to a fire, which many cowboy movies show in response to a dastardly act by the villain. The townsfolk form a human chain to carry a water source to fi re, as they could much more quickly move buckets up the chain instead of individuals running back and forth. Our pipeline icon is a sequence of pipes, with each section representing one stage of the pipeline.

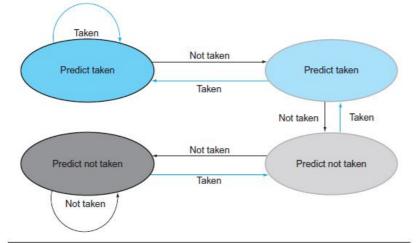

#### 6. Performance via prediction

Following the saying that it can be better to ask for forgiveness than to ask for permission, the next great idea is prediction. In some cases it can be faster on average to guess and start working rather than wait until you know for sure, assuming that the mechanism to recover from a misprediction is not too

expensive and your prediction is relatively accurate. We use the fortune-teller's crystal ball as our prediction icon.

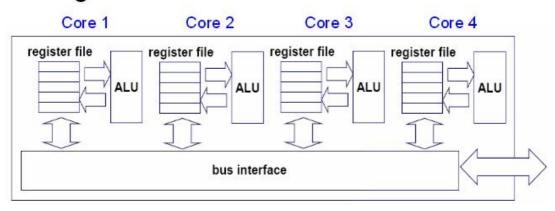

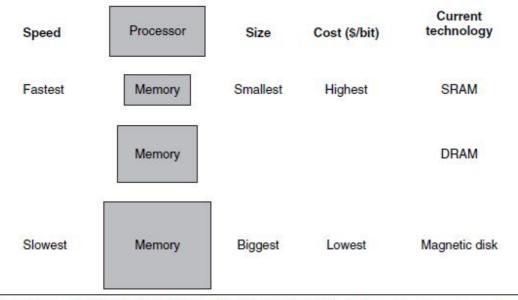

#### 7. Hierarchy of memories

**HIERARCHY** Programmers want memory to be fast, large, and cheap, as memory speed often shapes performance, capacity limits the size of problems that can be solved, and the cost of memory today is often the majority of computer cost. Architects have found that they can address these conflicting demands with a hierarchy of memories, with the fastest, smallest, and most expensive memory per bit at the top of the hierarchy and the slowest, largest, and cheapest per bit at the bottom. Caches give the programmer the illusion that main memory is nearly as fast as the top of the hierarchy and nearly as big and cheap as the bottom of the hierarchy. We use a layered triangle icon to represent the memory hierarchy. The shape indicates speed, cost, and size: the closer to the top, the faster and more expensive per bit the memory; the wider the base of the layer, the bigger the memory.

#### 8. Dependability via redundancy

**DEPENDABILITY** Computers not only need to be fast; they need to be dependable. Since any physical device can fail, we make systems dependable by including redundant components that can take over when a failure occurs and to help detect failures. We use the tractor-trailer as our icon, since the dual tires on each side of its rear axels allow the truck to continue driving even when one tire fails. (Presumably, the truck driver heads immediately to a repair facility so the fl at tire can be fixed, thereby restoring redundancy!)

#### COMPONENTS OF COMPUTER SYSTEM

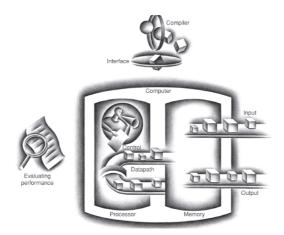

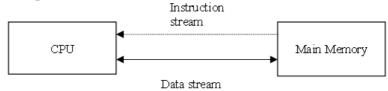

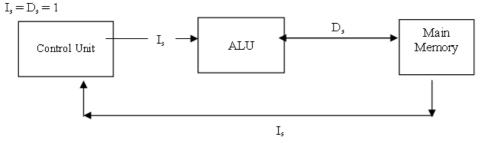

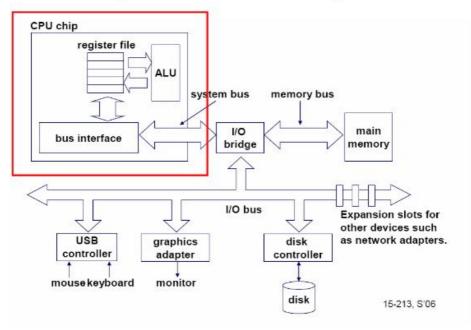

The five classic components of a computer are input, output, memory, datapath, and control, with the last two sometimes combined and called the processor. Figure 1.5 shows the standard rganization of a computer. Th is organization is independent of hardware technology: you can place every piece of every computer, past and present, into one of these five categories.

#### Through the Looking Glass

The most fascinating I/O device is probably the graphics display. Most personal mobile devices use liquid crystal displays (LCDs) to get a thin, low-power display. The LCD is not the source of light; instead, it controls the transmission of light. A typical LCD includes rod-shaped molecules in a liquid that form a twisting helix that bends light entering the display, from either a light source behind the display or less oft en from refl ected light. The rods straighten out when a current is applied and no longer bend the light. Since the liquid crystal material is between two screens polarized at 90 degrees, the light cannot pass through unless it is bent.

Today, most LCD displays use an active matrix that has a tiny transistor switch at each pixel to precisely control current and make sharper images. A red-green-blue mask associated with each dot on the display determines the intensity of the threecolor components in the fi nal image; in a color active matrix LCD, there are three transistor switches at each point.

The image is composed of a matrix of picture elements, or pixels, which can be represented as a matrix of bits, called a *bit map*. Depending on the size of the screen and the resolution, the display matrix in a typical tablet ranges in size from 1024 \_ 768 to 2048 \_ 1536. A color display might use 8 bits for each of the three colors (red, blue, and green), for 24 bits per pixel, permitting millions of diff erent colors to be displayed.

#### Touchscreen

While PCs also use LCD displays, the tablets and smartphones of the PostPC era have replaced the keyboard and mouse with touch sensitive displays, which has the wonderful user interface advantage of users pointing directly what they are interested in rather than indirectly with a mouse. While there are a variety of ways to implement a touch screen, many tablets today use capacitive sensing. Since people are electrical conductors, if an insulator like glass is covered with a transparent conductor, touching distorts the electrostatic fi eld of the screen, which results in a change in capacitance. Th is technology can allow multiple touches simultaneously, which allows gestures that can lead to attractive user interfaces.

#### **Opening the Box**

Figure 1.7 shows the contents of the Apple iPad 2 tablet computer. Unsurprisingly, of the fi ve classic components of the computer, I/O dominates this reading device. The list of I/O devices includes a capacitive multitouch LCD display, front facing camera, rear facing camera, microphone, headphone jack, speakers, accelerometer, gyroscope, Wi-Fi network, and Bluetooth network. The datapath, ontrol, and memory are a tiny portion of the components. Th e small rectangles in Figure 1.8 contain the devices that drive our advancing technology, called integrated circuits and nicknamed chips. Th e A5 package seen in the middle of in Figure 1.8 contains two ARM processors that operate with a clock rate

of 1 GHz. The *processor* is the active part of the computer, following the instructions of a program to the letter. It adds numbers, tests numbers, signals I/O devices to activate, and so on. Occasionally, people call the processor the CPU, for the more bureaucratic-sounding central processor unit.

#### Cache memory

Itconsists of a small, fast memory that acts as a buff er for the DRAM memory. (The nontechnical definition of *cache* is a safe place for hiding things.) Cache is built using a diff erent memory technology, static random access memory (SRAM). SRAM is faster but less dense, and hence more expensive, than DRAM (see Chapter 5). SRAM and DRAM are two layers of the memory hierarchy.

#### A Safe Place for Data

Th us far, we have seen how to input data, compute using the data, and display data. If we were to lose power to the computer, however, everything would be lost because the memory inside the computer is volatile—that is, when it loses power, it forgets. In contrast, a DVD disk doesn't forget the movie when you turn off the power to the DVD player, and is thus a nonvolatile memory technology.

#### **Communicating with Other Computers**

We've explained how we can input, compute, display, and save data, but there is still one missing item found in today's computers: computer networks. Just as the processor shown in Figure 1.5 is connected to memory and I/O devices, networks interconnect whole computers, allowing computer users to extend the power of computing by including communication. Networks have become so popular that they are the backbone of current computer systems; a new personal mobile device or server without a network interface would be ridiculed. Networked computers have several major advantages:

*Communication*: Information is exchanged between computers at high speeds.

*Resource sharing:* Rather than each computer having its own I/O devices, computers on the network can share I/O devices.

*Nonlocal access*: By connecting computers over long distances, users need not be near the computer they are using.

Networks vary in length and performance, with the cost of communication increasing according to both the speed of communication and the distance that information travels. Perhaps the most popular type of network is *Ethernet*. It can be up to a kilometer long and transfer at up to 40 gigabits per second.

# Technologies for Building Processors and Memory

Processors and memory have improved at an incredible rate, because computer designers have long embraced the latest in electronic technology to try to win the race to design a better computer. been used over time, with an estimate of the relative performance per unit cost for each technology. Since this technology shapes what computers will be able to do and how quickly they will evolve, we believe all computer professionals should be familiar with the basics of integrated circuits.

A transistor is simply an on/off switch controlled by electricity. The *integrated circuit* (IC) combined dozens to hundreds of transistors into a single chip. When Gordon Moore predicted the continuous doubling of resources, he was predicting the growth rate of the number of transistors per chip. To describe the tremendous increase in the number of transistors from hundreds to millions, the adjective *very large scale* is added to the term, creating the abbreviation *VLSI*, for very large-scale integrated circuit.

Th is rate of increasing integration has been remarkably stable. Figure 1.11 shows the growth in DRAM capacity since 1977. For decades, the industry has consistently quadrupled capacity every 3 years, resulting in an increase in excess of 16,000 times! To understand how manufacture integrated circuits, we start at the beginning. The manufacture of a chip begins with silicon, a substance found in sand. Because silicon does not conduct electricity well, it is called a semiconductor. With a special chemical process, it is possible to add materials to silicon that allow tiny areas to transform into one of three devices: Decellent conductors of electricity (using either microscopic copper or aluminum wire) been used over time, with an estimate of the relative performance per unit cost for each technology. Since this technology shapes what computers will be able to do and how quickly they will evolve, we believe all computer professionals should be familiar with the basics of integrated circuits.

A transistor is simply an on/off switch controlled by electricity. The *integrated circuit* (IC) combined dozens to hundreds of transistors into a single chip. When Gordon Moore predicted the continuous doubling of resources, he was predicting the growth rate of the number of transistors per chip. To describe the tremendous increase in the number of transistors from hundreds to millions, the adjective *very large scale* is added to the term, creating the abbreviation *VLSI*, for very large-scale integrated circuit. Th is rate of increasing integration has been remarkably stable. Figure 1.11 shows the growth in DRAM capacity since 1977. For decades, the industry has consistently quadrupled capacity every 3 years, resulting in an increase in excess of 16,000 times! To understand how manufacture integrated circuits, we start at the beginning. Th e manufacture of a chip begins with silicon, a substance found in sand. Because silicon does not conduct electricity well, it is called a semiconductor. With a special chemical process, it is possible to add materials to silicon that allow tiny areas to transform into one of three devices:

- Excellent conductors of electricity (using either microscopic copper or

- Excellent insulators from electricity (like plastic sheathing or glass)

- Areas that can conduct or insulate under special conditions (as a switch)

Transistors fall in the last category. A VLSI circuit, then, is just billions of combinations of conductors, insulators, and switches manufactured in a single small package.aluminum wire)

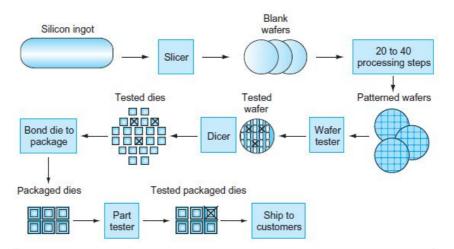

**FIGURE 1.12** The chip manufacturing process. After being sliced from the silicon ingot, blank wafers are put through 20 to 40 steps to create patterned wafers (see Figure 1.13). These patterned wafers are then tested with a wafer tester, and a map of the good parts is made. Then, the wafers are diced into dies (see Figure 1.9). In this figure, one wafer produced 20 dies, of which 17 passed testing. (X means the die is bad.) The yield of good dies in this case was 17/20, or 85%. These good dies are then bonded into packages and tested one more time before shipping the packaged parts to customers. One bad packaged part was found in this final test.

Elaboration: The cost of an integrated circuit can be expressed in three simple equations:

Cost per die =

$$\frac{\text{Cost per wafer}}{\text{Dies per wafer } \times \text{yield}}$$

Dies per wafer  $\approx \frac{\text{Wafer area}}{\text{Die area}}$

Yield =  $\frac{1}{(1 + (\text{Defects per area} \times \text{Die area}/2))^2}$

The first equation is straightforward to derive. The second is an approximation, since it does not subtract the area near the border of the round wafer that cannot accommodate the rectangular dies (see Figure 1.13). The final equation is based on empirical observations of yields at integrated circuit factories, with the exponent related to the number of critical processing steps.

Hence, depending on the defect rate and the size of the die and wafer, costs are generally not linear in the die area.

#### Performance

#### **Defining Performance**

When we say one computer has better performance than another, what do we mean? Although this question might seem simple, an analogy with passenger airplanes shows how subtle the question of performance can be. Figure 1.14 lists some typical passenger airplanes, together with their cruising speed, range, and capacity. If we wanted to know which of the planes in this table had the best performance, we would first need to define performance. For example, considering different measures of performance, we see that the plane with the highest cruising speed was the Concorde (retired from service in 2003), the plane with the longest range is the DC-8, and the plane with the largest capacity is the 747.

| Airplane         | Passenger<br>capacity | Cruising range<br>(miles) | Cruising speed<br>(m.p.h.) | Passenger throughput<br>(passengers <sub>x</sub> m.p.h.) |

|------------------|-----------------------|---------------------------|----------------------------|----------------------------------------------------------|

| Boeing 777       | 375                   | 4630                      | 610                        | 228,750                                                  |

| Boeing 747       | 470                   | 4150                      | 610                        | 286,700                                                  |

| BAC/Sud Concorde | 132                   | 4000                      | 1350                       | 178,200                                                  |

| Douglas DC-8-50  | 146                   | 8720                      | 544                        | 79,424                                                   |

**FIGURE 1.14** The capacity, range, and speed for a number of commercial airplanes. The last column shows the rate at which the airplane transports passengers, which is the capacity times the cruising speed (ignoring range and takeoff and landing times).

#### **Throughput and Response Time**

Do the following changes to a computer system increase throughput, decrease response time, or both?

1. Replacing the processor in a computer with a faster version

2. Adding additional processors to a system that uses multiple processors for separate tasks—for example, searching the web Decreasing response time almost always improves throughput. Hence, in case

1, both response time and throughput are improved. In case 2, no one task gets work done faster, so only throughput increases. If, however, the demand for processing in the second case was almost as large as the throughput, the system might force requests to queue up. In this case, increasing the throughput could also improve response time, since it would reduce the waiting time in the queue. Th us, in many real computer systems, changing either execution time or throughput oft en aff ects the other. In discussing the performance of computers, we will be primarily concerned with response time for the first few chapters. To maximize performance, we want to minimize response time or execution time for a computer X:

$Performance_X = \frac{1}{Execution time_X}$

This means that for two computers X and Y, if the performance of X is greater than the performance of Y, we have

| Performance <sub>x</sub>  | > | Performancey                |

|---------------------------|---|-----------------------------|

| 1                         | ~ | 1                           |

| Execution time $_{\rm X}$ | - | Execution time <sub>Y</sub> |

| Execution time $_{\rm Y}$ | > | Execution time $_{\rm X}$   |

That is, the execution time on Y is longer than that on X, if X is faster than Y.

#### **Relative Performance**

If computer A runs a program in 10 seconds and computer B runs the same program in 15 seconds, how much faster is A than B?

We know that A is n times as fast as B if

$\frac{\text{Performance}_{A}}{\text{Performance}_{B}} = \frac{\text{Execution time}_{B}}{\text{Execution time}_{A}} = n$

Thus the performance ratio is

$$\frac{15}{10} = 1.5$$

and A is therefore 1.5 times as fast as B.

In the above example, we could also say that computer B is 1.5 times *slower than* computer A, since

$$\frac{\text{Performance}_{\text{A}}}{\text{Performance}_{\text{B}}} = 1.5$$

means that

$\frac{\text{Performance}_{\text{A}}}{1.5} = \text{Performance}_{\text{B}}$

# **The Power Wall**

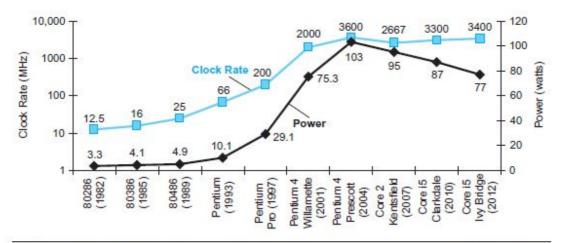

Figure 1.16 shows the increase in clock rate and power of eight generations of Intel microprocessors over 30 years. Both clock rate and power increased rapidly for decades, and then flattened off recently. The reason they grew together is that they are correlated, and the reason for their recent slowing is that we have run into the practical power limit for cooling commodity microprocessors.

FIGURE 1.16 Clock rate and Power for Intel x86 microprocessors over eight generations and 25 years. The Pentium 4 made a dramatic jump in clock rate and power but less so in performance. The Prescott thermal problems led to the abandonment of the Pentium 4 line. The Core 2 line reverts to a simpler pipeline with lower clock rates and multiple processors per chip. The Core i5 pipelines follow in its footsteps.

The dominant technology for integrated circuits is called CMOS (complementary metal oxide semiconductor). For CMOS, the primary source of energy consumption is so-called dynamic energy—that is, energy that is consumed when transistors switch states from 0 to 1 and vice versa. The dynamic energy depends on the capacitive loading of each transistor and the voltage applied:

Energy  $\propto$  Capacitive load  $\times$  Voltage<sup>2</sup>

This equation is the energy of a pulse during the logic transition of  $0 \rightarrow 1 \rightarrow 0$  or  $1 \rightarrow 0 \rightarrow 1$ . The energy of a single transition is then

Energy  $\propto 1/2 \times Capacitive load \times Voltage^2$

The power required per transistor is just the product of energy of a transition and the frequency of transitions:

Power  $\propto 1/2 \times Capacitive load \times Voltage^2 \times Frequency switched$

Frequency switched is a function of the clock rate. The capacitive load per transistor is a function of both the number of transistors connected to an output (called the *fanout*) and the technology, which determines the capacitance of both wires and transistors.

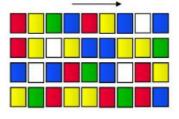

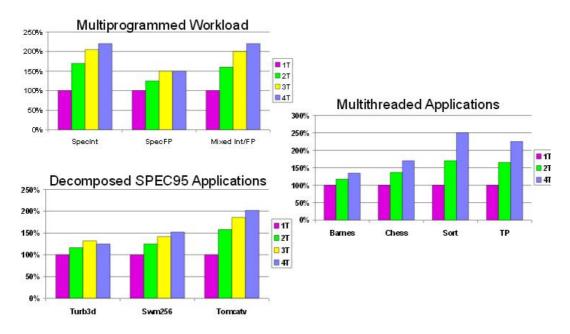

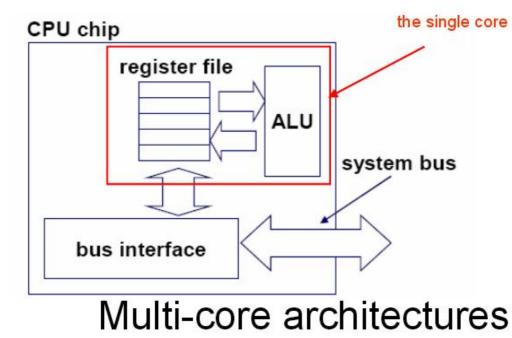

#### The Sea Change: The Switch from Uniprocessors to Multiprocessors

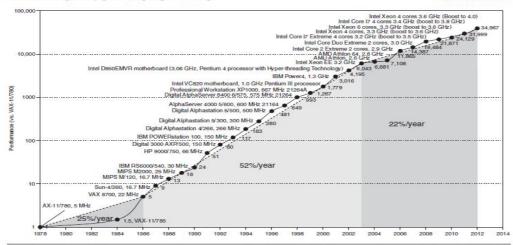

The power limit has forced a dramatic change in the design of microprocessors. Figure 1.17 shows the improvement in response time of programs for desktop microprocessors over time. Since 2002, the rate has slowed from a factor of 1.5 per year to a factor of 1.2 per year.

Rather than continuing to decrease the response time of a single program running on the single processor, as of 2006 all desktop and server companies are shipping microprocessors with multiple processors per chip, where the benefit is oft en more on throughput than on response time. To reduce confusion between the words processor and microprocessor, companies refer to processors as "cores," and such microprocessors are generically called multicore microprocessors.

Hence, a "quadcore" microprocessor is a chip that contains four processors or four cores. In the past, programmers could rely on innovations in hardware, architecture, and compilers to double performance of their programs every 18 months without having to change a line of code. Today, for programmers to get significant improvement in response time, they need to rewrite their programs to take advantage of multiple processors. Moreover, to get the historic benefit of running faster on new microprocessors, programmers will have to continue to improve performance of their code as the number of cores increases.

To reinforce how the soft ware and hardware systems work hand in hand, we use a special section, *Hardware/Soft ware Interface*, throughout the book, with the first one appearing below. These elements summarize important insights at this critical interface.

Hardware/

Software

Interface

**Parallelism** has always been critical to performance in computing, but it was often hidden. Chapter 4 will explain **pipelining**, an elegant technique that runs programs faster by overlapping the execution of instructions. This is one example of *instruction-level parallelism*, where the parallel nature of the hardware is abstracted away so the programmer and compiler can think of the hardware as executing instructions sequentially.

Forcing programmers to be aware of the parallel hardware and to explicitly rewrite their programs to be parallel had been the "third rail" of computer architecture, for companies in the past that depended on such a change in behavior failed (see Section 6.15). From this historical perspective, it's startling that the whole IT industry has bet its future that programmers will finally successfully switch to explicitly parallel programming.

FIGURE 1.17 Growth in processor performance since the mid-1980s. This chart plots performance relative to the VAX 11/780 as measured by the SPECint benchmarks (see Section 1.10). Prior to the mid-1980s, processor performance growth was largely technologydriven and averaged about 25% per year. The increase in growth to about 52% since then is attributable to more advanced architectural and organizational ideas. The higher annual performance improvement of 52% since the mid-1980s meant performance was about a factor of seven higher in 2002 than it would have been had it stayed at 25%. Since 2002, the limits of power, available instruction-level parallelism, and long memory latency have slowed uniprocessor performance recently, to about 22% per year.

#### **Operations of the Computer Hardware**

Every computer must be able to perform arithmetic. The MIPS assembly language notation add a, b, c instructs a computer to add the two variables b and c and to put their sum in a.

This notation is rigid in that each MIPS arithmetic instruction performs only one operation and must always have exactly three variables. For example, suppose we want to place the sum of four variables b, c, d, and e into variable a. (In this section we are being deliberately vague about what a "variable" is; in the next section we'll explain in detail.)

The following sequence of instructions adds the four variables:

add a, b, c # The sum of b and c is placed in a

add a, a, d # The sum of b, c, and d is now in a

add a, a, e # The sum of b, c, d, and e is now in a

Thus, it takes three instructions to sum the four variables. The words to the right of the sharp symbol (#) on each line above are *comments* for the human reader, so the computer ignores them.

| Category         | Instruction                         | Example             | Meaning                                     | Comments                               |

|------------------|-------------------------------------|---------------------|---------------------------------------------|----------------------------------------|

|                  | add                                 | add \$s1,\$s2,\$s3  | \$s1 = \$s2 + \$s3                          | Three register operands                |

| Arithmetic       | subtract                            | sub \$s1,\$s2,\$s3  | \$s1 = \$s2 - \$s3                          | Three register operands                |

|                  | add immediate                       | addi \$s1,\$s2,20   | \$s1 = \$s2 + 20                            | Used to add constants                  |

|                  | load word                           | 1w \$s1,20(\$s2)    | \$s1 = Memory[\$s2 + 20]                    | Word from memory to register           |

|                  | store word                          | sw \$s1,20(\$s2)    | Memory[\$s2 + 20] = \$s1                    | Word from register to memory           |

|                  | load half                           | 1h \$s1,20(\$s2)    | \$s1 = Memory[\$s2 + 20]                    | Halfword memory to register            |

|                  | load half unsigned                  | 1hu \$s1,20(\$s2)   | \$s1 = Memory[\$s2 + 20]                    | Halfword memory to register            |

| 200              | store half                          | sh \$s1,20(\$s2)    | Memory[\$s2 + 20] = \$s1                    | Halfword register to memory            |

| Data<br>transfer | load byte                           | 1b \$s1,20(\$s2)    | \$s1 = Memory[\$s2 + 20]                    | Byte from memory to register           |

| transier         | load byte unsigned                  | 1bu \$s1,20(\$s2)   | \$s1 = Memory[\$s2 + 20]                    | Byte from memory to register           |

|                  | store byte                          | sb \$s1,20(\$s2)    | Memory[\$s2 + 20] = \$s1                    | Byte from register to memory           |

|                  | load linked word                    | 11 \$s1,20(\$s2)    | \$s1 = Memory[\$s2 + 20]                    | Load word as 1st half of atomic swap   |

|                  | store condition. word               | sc \$s1,20(\$s2)    | Memory[\$s2+20]=\$s1;\$s1=0 or 1            | Store word as 2nd half of atomic swa   |

|                  | load upper immed.                   | lui \$s1,20         | \$s1 = 20 * 2 <sup>16</sup>                 | Loads constant in upper 16 bits        |

|                  | and                                 | and \$s1,\$s2,\$s3  | \$s1 = \$s2 & \$s3                          | Three reg. operands; bit-by-bit AND    |

|                  | or                                  | or \$s1,\$s2,\$s3   | \$s1 = \$s2   \$s3                          | Three reg. operands; bit-by-bit OR     |

|                  | nor                                 | nor \$s1,\$s2,\$s3  | \$s1 = ~ (\$s2   \$s3)                      | Three reg. operands; bit-by-bit NOR    |

| Logical          | and immediate                       | andi \$s1,\$s2,20   | \$s1 = \$s2 & 20                            | Bit-by-bit AND reg with constant       |

|                  | or immediate                        | ori \$s1,\$s2,20    | \$s1 = \$s2   20                            | Bit-by-bit OR reg with constant        |

|                  | shift left logical                  | s11 \$s1,\$s2,10    | \$s1 = \$s2 << 10                           | Shift left by constant                 |

|                  | shift right logical                 | srl \$sl,\$s2,10    | \$s1 = \$s2 >> 10                           | Shift right by constant                |

|                  | branch on equal                     | beq \$s1,\$s2,25    | if (\$s1 == \$s2) go to<br>PC + 4 + 100     | Equal test; PC-relative branch         |

|                  | branch on not equal                 | bne \$s1,\$s2,25    | if (\$s1!= \$s2) go to<br>PC + 4 + 100      | Not equal test; PC-relative            |

| Conditional      | set on less than                    | slt \$s1,\$s2,\$s3  | if (\$s2 < \$s3) \$s1 = 1;<br>else \$s1 = 0 | Compare less than; for beq, bne        |

| branch           | set on less than unsigned           | sltu \$sl,\$s2,\$s3 | if (\$s2 < \$s3) \$s1 = 1;<br>else \$s1 = 0 | Compare less than unsigned             |

|                  | set less than<br>immediate          | slti \$sl,\$s2,20   | if (\$s2 < 20) \$s1 = 1;<br>else \$s1 = 0   | Compare less than constant             |

|                  | set less than<br>immediate unsigned | sltiu \$sl,\$s2,20  | if (\$s2 < 20) \$s1 = 1;<br>else \$s1 = 0   | Compare less than constant<br>unsigned |

#### MIPS ASSEMBLY LANGUAGE CODE

#### **Compliing Two C Assignment Statements Into MIPS**

This segment of a C program contains the five variables a, b, c, d, and e. Since Java evolved from C, this example and the next few work for either high-level programming language:

a = b + c; d = a - e;

The translation from C to MIPS assembly language instructions is performed by the *compiler*. Show the MIPS code produced by a compiler.

A MIPS instruction operates on two source operands and places the result in one destination operand. Hence, the two simple statements above compile directly into these two MIPS assembly language instructions:

add a, b, c sub d, a, e

#### **Operands of the Computer Hardware**

One major difference between the variables of a programming language and registers is the limited number of registers, typically 32 on current computers, like MIPS. (See Section 2.21 for the history of the number of registers.) Thus, continuing in our top-down, stepwise evolution of the symbolic representation of the MIPS language, in this section we have added the restriction that the three operands of MIPS arithmetic instructions must each be chosen from one of the 32 32-bit registers. The reason for the limit of 32 registers may be found in the second of our three underlying design principles of hardware technology:

#### Design Principle 2: Smaller is faster.

A very large number of registers may increase the clock cycle time simply because it takes electronic signals longer when they must travel farther. Guidelines such as "smaller is faster" are not absolutes; 31 registers may not be faster than 32. Yet, the truth behind such observations causes computer designers to take them seriously. In this case, the designer must balance the craving of programs for more registers with the designer's desire to keep the clock cycle fast. Another reason for not using more than 32 is the number of bits it would take in the instruction format, as Section 2.5 demonstrates.

#### **Compliing a C Assignment Using Registers**

It is the compiler's job to associate program variables with registers. Take, for instance, the assignment statement from our earlier example:

f = (g + h) - (i + j);

The variables f, g, h, i, and j are assigned to the registers \$\$0, \$\$1, \$\$2, \$\$3, and \$\$4, respectively. What is the compiled MIPS code?

The compiled program is very similar to the prior example, except we replace the variables with the register names mentioned above plus two temporary registers, t0 and t1, which correspond to the temporary variables above:

add \$t0,\$s1,\$s2 # register \$t0 contains g + h add \$t1,\$s3,\$s4 # register \$t1 contains i + j sub \$s0,\$t0,\$t1 # f gets \$t0 - \$t1, which is (g + h)-(i + j)

#### **Memory Operands**

Recall the five components of a computer introduced in Chapter 1 and repeated on page 61. The processor can keep only a small amount of data in registers, but computer memory contains billions of data elements. Hence, data structures (arrays and structures) are kept in memory.

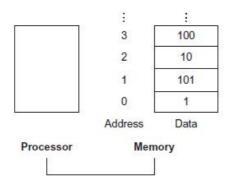

As explained above, arithmetic operations occur only on registers in MIPS instructions; thus, MIPS must include instructions that transfer data between memory and registers. Such instructions are called **data transfer instructions**. To access a word in memory, the instruction must supply the memory **address**. Memory is just a large, single-dimensional array, with the address acting as the index to that array, starting at 0. For example, in Figure 2.2, the address of the third data element is 2, and the value of Memory [2] is 10.

FIGURE 2.2 Memory addresses and contents of memory at those locations. If these elements were words, these addresses would be incorrect, since MIPS actually uses byte addressing, with each word representing four bytes. Figure 2.3 shows the memory addressing for sequential word addresses.

#### **Logical Operations**

Although the first computers operated on full words, it soon became clear that it was useful to operate on fields of bits within a word or even on individual bits. Examining characters within a word, each of which is stored as 8 bits, is one example of such an operation (see Section 2.9). It follows that operations were added to programming languages and instruction set architectures to simplify, among other things, the packing and unpacking of bits into words. Th ese instructions are called logical operations. Figure 2.8 shows logical operations in C, Java, and MIPS.

| Logical operations | C operators | Java operators | MIPS Instructions |

|--------------------|-------------|----------------|-------------------|

| Shift left         | <<          | <<             | s11               |

| Shift right        | >>          | >>>            | srl               |

| Bit-by-bit AND     | &           | &              | and, andi         |

| Bit-by-bit OR      | 1           | 1              | or.ori            |

| Bit-by-bit NOT     | ~           | ~              | nor               |

FIGURE 2.8 C and Java logical operators and their corresponding MIPS instructions. MIPS implements NOT using a NOR with one operand being zero.

The first class of such operations is called *shift s*. They move all the bits in a word to the left or right, filling the emptied bits with 0s. For example, if register \$s0 contained

0000 0000 0000 0000 0000 0000 0000 1001two = 9ten

and the instruction to shift left by 4 was executed, the new value would be:

0000 0000 0000 0000 0000 1001 0000two = 144ten

The dual of a shift left is a shift right. The actual name of the two MIPS shift instructions are called *shift left logical* (s11) and *shift right logical* (sr1). The following instruction performs the operation above, assuming that the original value was in register s0 and the result should go in register t2:

sll \$t2.\$s0.4 # reg \$t2 = reg \$s0 << 4 bits

We delayed explaining the *shamt* field in the R-format. Used in shift instructions, it stands for *shift amount*. Hence, the machine language version of the instruction above is

| op | rs | rt | rd | shamt | funct |

|----|----|----|----|-------|-------|

| 0  | 0  | 16 | 10 | 4     | 0     |

### Instructions for Making Decisions

What distinguishes a computer from a simple calculator is its ability to make decisions. Based on the input data and the values created during computation, different instructions execute. Decision making is commonly represented in programming languages using the *if* statement, sometimes combined with *go to* statements and labels. MIPS assembly language includes two decision-making instructions, similar to an *if* statement with a *go to*. The first instruction is

```

beq register1, register2, L1

```

This instruction means go to the statement labeled L1 if the value in register1 equals the value in register2. The mnemonic beq stands for *branch if equal*. The second instruction is

```

bne register1, register2, L1

```

It means go to the statement labeled L1 if the value in register1 does *not* equal the value in register2. The mnemonic bne stands for *branch if not equal*. These two instructions are traditionally called conditional branches.

#### **Compiling If-then-else Into Conditional Branches**

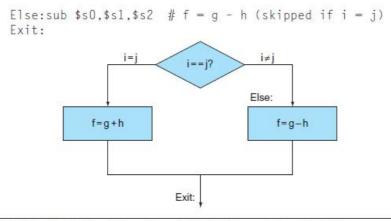

In the following code segment, f, g, h, i, and j are variables. If the five variables f through j correspond to the five registers \$50 through \$54, what is the compiled MIPS code for this C *if* statement?

if (i == j) f = g + h; else f = g - h;

Figure 2.9 shows a flowchart of what the MIPS code should do. The first expression compares for equality, so it would seem that we would want the branch if registers are equal instruction (beq). In general, the code will be more efficient if we test for the opposite condition to branch over the code that performs the subsequent *then* part of the *if* (the label Else is defined below) and so we use the branch if registers are *not* equal instruction (bne):

bne \$s3,\$s4,Else ∦ go to Else if i ≠ j

The next assignment statement performs a single operation, and if all the operands are allocated to registers, it is just one instruction:

add s0, s1, s2 # f = g + h (skipped if i  $\neq$  j) We now need to go to the end of the *if* statement. This example introduces another kind of branch, often called an *unconditional branch*. This instruction says that the processor always follows the branch. To distinguish between conditional and unconditional branches, the MIPS name for this type of instruction is *jump*, abbreviated as j (the label Exit is defined below).

```

j Exit # go to Exit

```

The assignment statement in the *else* portion of the *if* statement can again be compiled into a single instruction. We just need to append the label Else to this instruction. We also show the label Exit that is after this instruction, showing the end of the *if-then-else* compiled code:

FIGURE 2.9 Illustration of the options in the if statement above. The left box corresponds to the *then* part of the *if* statement, and the right box corresponds to the *else* part.

#### Loops

Decisions are important both for choosing between two alternatives—found in *if* statements—and for iterating a computation—found in loops. The same assembly instructions are the building blocks for both cases.

#### **Compliing a while Loop in C**

Here is a traditional loop in C:

while (save[i] == k) i += 1;

Assume that i and k correspond to registers \$\$3 and \$\$5 and the base of the array save is in \$\$6. What is the MIPS assembly code corresponding to this C segment?

The first step is to load save[i] into a temporary register. Before we can load save[i] into a temporary register, we need to have its address. Before we can add i to the base of array save to form the address, we must multiply the index i by 4 due to the byte addressing problem. Fortunately, we can use shift left logical, since shifting left by 2 bits multiplies by  $2^2$  or 4 (see page 88 in the prior section). We need to add the label Loop to it so that we can branch back to that instruction at the end of the loop:

Loop: sll \$t1,\$s3,2 # Temp reg \$t1 = i \* 4

To get the address of save[i], we need to add \$t1 and the base of save in \$s6:

add \$t1,\$t1,\$s6 # \$t1 = address of save[i]

Now we can use that address to load save[i] into a temporary register:

lw \$t0,0(\$t1)# Temp reg \$t0 = save[i] The next instruction performs the loop test, exiting if save[i] \neq k:

bne \$t0,\$s5, Exit ∦ go to Exit if save[i] ≠ k

The next instruction adds 1 to i:

addi \$s3,\$s3,1 # i = i + 1

The end of the loop branches back to the *while* test at the top of the loop. We just add the Exit label after it, and we're done:

j Loop # go to Loop Exit:

(See the exercises for an optimization of this sequence.)

#### **Case/Switch Statement**

Most programming languages have a *case* or *switch* statement that allows the programmer to select one of many alternatives depending on a single value. The simplest way to implement *switch* is via a sequence of conditional tests, turning the *switch* statement into a chain of *if-then-else* statements.

Sometimes the alternatives may be more efficiently encoded as a table of addresses of alternative instruction sequences, called a **jump address table** or **jump table**, and the program needs only to index into the table and then jump to the appropriate sequence. The jump table is then just an array of words containing addresses that correspond to labels in the code. The program loads the appropriate entry from the jump table into a register. It then needs to jump using the address in the register. To support such situations, computers like MIPS include a *jump register* instruction (jr), meaning an unconditional jump to the address specified in a register. Then it jumps to the proper address using this instruction. We'll see an even more popular use of jr in the next section.

#### MIPS Addressing for 32-bit Immediates and Addresses

Although keeping all MIPS instructions 32 bits long simplifi es the hardware, there are times where it would be convenient to have a 32-bit constant or 32-bit address. This section starts with the general solution for large constants, and then shows the optimizations for instruction addresses used in branches and jumps.

#### **32-Bit Immediate Operands**

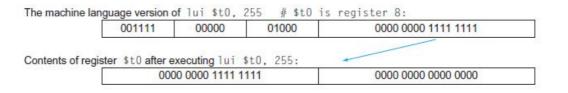

Although constants are frequently short and fit into the 16-bit field, sometimes they are bigger. The MIPS instruction set includes the instruction *load upper immediate* (lui) specifically to set the upper 16 bits of a constant in a register, allowing a subsequent instruction to specify the lower 16 bits of the constant. Figure 2.17 shows the operation of lui.

#### Loading a 32-Bit Constant

FIGURE 2.17 The effect of the lui instruction. The instruction lui transfers the 16-bit immediate constant field value into the leftmost 16 bits of the register, filling the lower 16 bits with 0s.

#### Addressing in Branches and Jumps

The MIPS jump instructions have the simplest addressing. They use the final MIPS instruction format, called the *J*-*type*, which consists of 6 bits for the operation field and the rest of the bits for the address field. Thus,

j 10000 # go to location 10000

could be assembled into this format (it's actually a bit more complicated, as we will see):

| 2      | 10000   |

|--------|---------|

| 6 bits | 26 bits |

where the value of the jump opcode is 2 and the jump address is 10000.

Unlike the jump instruction, the conditional branch instruction must specify two operands in addition to the branch address. Thus,

bne \$s0,\$s1,Exit # go to Exit if \$s0 ≠ \$s1

is assembled into this instruction, leaving only 16 bits for the branch address:

| 5      | 16     | 17     | Exit    |  |

|--------|--------|--------|---------|--|

| 6 bits | 5 bits | 5 bits | 16 bits |  |

If addresses of the program had to fit in this 16-bit field, it would mean that no program could be bigger than  $2^{16}$ , which is far too small to be a realistic option today. An alternative would be to specify a register that would always be added to the branch address, so that a branch instruction would calculate the following:

Program counter = Register + Branch address

This sum allows the program to be as large as  $2^{32}$  and still be able to use conditional branches, solving the branch address size problem. Then the question is, which register?

The answer comes from seeing how conditional branches are used. Conditional branches are found in loops and in *if* statements, so they tend to branch to a nearby instruction. For example, about half of all conditional branches in SPEC benchmarks go to locations less than 16 instructions away. Since the *program counter* (PC) contains the address of the current instruction, we can branch within  $\pm 2^{15}$  words of the current instruction if we use the PC as the register to be added to the address. Almost all loops and *if* statements are much smaller than  $2^{16}$  words, so the PC is the ideal choice.

This form of branch addressing is called PC-relative addressing. As we shall see in Chapter 4, it is convenient for the hardware to increment the PC early to point to the next instruction. Hence, the MIPS address is actually relative to the address of the following instruction (PC + 4) as opposed to the current instruction (PC). It is yet another example of making the common case fast, which in this case is addressing nearby instructions.

### Showing Branch Offset in Machine Language

The while loop on pages 92-93 was compiled into this MIPS assembler code:

If we assume we place the loop starting at location 80000 in memory, what is the MIPS machine code for this loop?

The assembled instructions and their addresses are:

| 80000 | 0  | 0     | 19 | 9 | 2 | 0  |  |

|-------|----|-------|----|---|---|----|--|

| 80004 | 0  | 9     | 22 | 9 | 0 | 32 |  |

| 80008 | 35 | 9     | 8  | 0 |   |    |  |

| 80012 | 5  | 8     | 21 | 2 |   |    |  |

| 80016 | 8  | 19    | 19 | 1 |   |    |  |

| 80020 | 2  | 20000 |    |   |   |    |  |

| 00004 |    | 8     |    |   |   |    |  |

80024

### MIPS Addressing Mode Summary

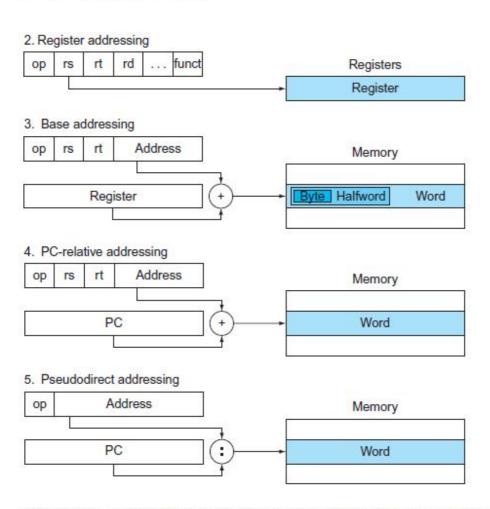

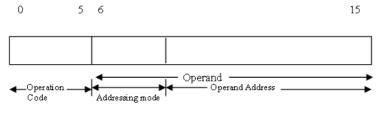

Multiple forms of addressing are generically called **addressing modes**. Figure 2.18 shows how operands are identified for each addressing mode. The MIPS addressing modes are the following:

1. Immediate addressing, where the operand is a constant within the instruction itself

2. Register addressing, where the operand is a register

3. *Base* or *displacement addressing*, where the operand is at the memory location whose address is the sum of a register and a constant in the instruction

4. *PC-relative addressing*, where the branch address is the sum of the PC and a constant in the instruction

5. *Pseudodirect addressing*, where the jump address is the 26 bits of the instruction concatenated with the upper bits of the PC

#### 1. Immediate addressing

op rs rt Immediate

**FIGURE 2.18 Illustration of the five MIPS addressing modes.** The operands are shaded in color. The operand of mode 3 is in memory, whereas the operand for mode 2 is a register. Note that versions of load and store access bytes, halfwords, or words. For mode 1, the operand is 16 bits of the instruction itself. Modes 4 and 5 address instructions in memory, with mode 4 adding a 16-bit address shifted left 2 bits to the PC and mode 5 concatenating a 26-bit address shifted left 2 bits with the 4 upper bits of the PC. Note that a single operation can use more than one addressing mode. Add, for example, uses both immediate (addi) and register (add) addressing.

#### UNIT II ARITHMETIC OPERATIONS

### Introduction

Computer words are composed of bits; thus, words can be represented as binary numbers. Chapter 2 shows that integers can be represented either in decimal or binary form, but what about the other numbers that commonly occur? For example:

- What about fractions and other real numbers?

- What happens if an operation creates a number bigger than can be represented?

- And underlying these questions is a mystery: How does hardware really multiply or divide numbers?

The goal of this chapter is to unravel these mysteries including representation of real numbers, arithmetic algorithms, hardware that follows these algorithms, and the implications of all this for instruction sets. These insights may explain quirks that you have already encountered with computers. Moreover, we show how to use this knowledge to make arithmetic-intensive programs go much faster.

# Addition and Subtraction

Addition is just what you would expect in computers. Digits are added bit by bit from right to left, with carries passed to the next digit to the left, just as you would do by hand. Subtraction uses addition: the appropriate operand is simply negated before being added.

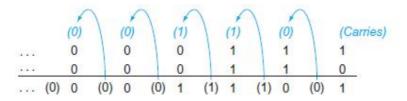

#### Binary Addition and Subtraction

Let's try adding 6<sub>ten</sub> to 7<sub>ten</sub> in binary and then subtracting 6<sub>ten</sub> from 7<sub>ten</sub> in binary.

The 4 bits to the right have all the action; Figure 3.1 shows the sums and carries. The carries are shown in parentheses, with the arrows showing how they are passed.

Subtracting 6<sub>ten</sub> from 7<sub>ten</sub> can be done directly:

**FIGURE 3.1** Binary addition, showing carries from right to left. The rightmost bit adds 1 to 0, resulting in the sum of this bit being 1 and the carry out from this bit being 0. Hence, the operation for the second digit to the right is 0 + 1 + 1. This generates a 0 for this sum bit and a carry out of 1. The third digit is the sum of 1 + 1 + 1, resulting in a carry out of 1 and a sum bit of 1. The fourth bit is 1 + 0 + 0, yielding a 1 sum and no carry.

|   | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | $0111_{two}$        | = | 7 <sub>ten</sub> |

|---|------|------|------|------|------|------|------|---------------------|---|------------------|

| - | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0110 <sub>two</sub> | = | 6 <sub>ten</sub> |

| = | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0001 <sub>two</sub> | = | 1 <sub>ten</sub> |

#### or via addition using the two's complement representation of -6:

|   | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0111 <sub>two</sub> | = | 7 <sub>ten</sub>  |

|---|------|------|------|------|------|------|------|---------------------|---|-------------------|

| + | 1111 | 1111 | 1111 | 1111 | 1111 | 1111 | 1111 | 1010 <sub>two</sub> | = | -6 <sub>ten</sub> |

| = | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0001 <sub>two</sub> | = | 1 <sub>ten</sub>  |

| Operation | Operand A | Operand B | Result<br>Indicating overflow |

|-----------|-----------|-----------|-------------------------------|

| A + B     | ≥0        | ≥0        | < 0                           |

| A + B     | < 0       | < 0       | ≥0                            |

| A – B     | ≥0        | < 0       | < 0                           |

| A – B     | < 0       | ≥ 0       | ≥0                            |

#### FIGURE 3.2 Overflow conditions for addition and subtraction.

We have just seen how to detect overflow for two's complement numbers in a computer. What about overflow with unsigned integers? Unsigned integers are commonly used for memory addresses where overflows are ignored.

The computer designer must therefore provide a way to ignore overflow in some cases and to recognize it in others. The MIPS solution is to have two kinds of arithmetic instructions to recognize the two choices:

- Add (add), add immediate (addi), and subtract (sub) cause exceptions on overflow.

- Add unsigned (addu), add immediate unsigned (addiu), and subtract unsigned (subu) do not cause exceptions on overflow.

Because C ignores overflows, the MIPS C compilers will always generate the unsigned versions of the arithmetic instructions addu, addiu, and subu, no matter what the type of the variables. The MIPS Fortran compilers, however, pick the appropriate arithmetic instructions, depending on the type of the operands.

Appendix B describes the hardware that performs addition and subtraction, which is called an Arithmetic Logic Unit or ALU.

# Multiplication

Now that we have completed the explanation of addition and subtraction, we are ready to build the more vexing operation of multiplication.

First, let's review the multiplication of decimal numbers in longhand to remind ourselves of the steps of multiplication and the names of the operands. For reasons that will become clear shortly, we limit this decimal example to using only the digits 0 and 1. Multiplying  $1000_{ten}$  by  $1001_{ten}$ :

| Multiplicand |      | 1000 <sub>ten</sub>    |  |  |  |

|--------------|------|------------------------|--|--|--|

| Multiplier   | Х    | 1001                   |  |  |  |

|              |      | 1000                   |  |  |  |

|              |      | 0000                   |  |  |  |

|              |      | 0000                   |  |  |  |

|              | 1000 |                        |  |  |  |

| Product      |      | 1001000 <sub>ten</sub> |  |  |  |

The first operand is called the *multiplicand* and the second the *multiplier*. The final result is called the *product*. As you may recall, the algorithm learned in grammar school is to take the digits of the multiplier one at a time from right to left, multiplying the multiplicand by the single digit of the multiplier, and shifting the intermediate product one digit to the left of the earlier intermediate products.

In this example, we restricted the decimal digits to 0 and 1. With only two choices, each step of the multiplication is simple:

- Just place a copy of the multiplicand (1 × multiplicand) in the proper place if the multiplier digit is a 1, or

- 2. Place 0 (0  $\times$  multiplicand) in the proper place if the digit is 0.

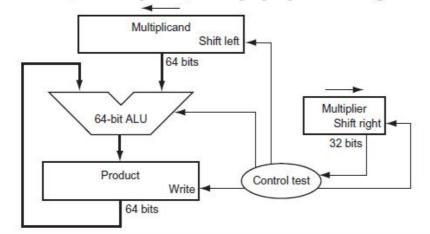

**FIGURE 3.3 First version of the multiplication hardware.** The Multiplicand register, ALU, and Product register are all 64 bits wide, with only the Multiplier register containing 32 bits. (Appendix B describes ALUs.) The 32-bit multiplicand starts in the right half of the Multiplicand register and is shifted left 1 bit on each step. The multiplier is shifted in the opposite direction at each step. The algorithm starts with the product initialized to 0. Control decides when to shift the Multiplicand and Multiplier registers and when to write new values into the Product register.

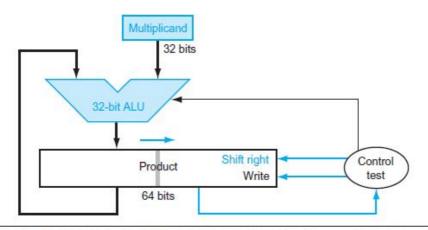

FIGURE 3.5 Refined version of the multiplication hardware. Compare with the first version in Figure 3.3. The Multiplicand register, ALU, and Multiplier register are all 32 bits wide, with only the Product register left at 64 bits. Now the product is shifted right. The separate Multiplier register also disappeared. The multiplier is placed instead in the right half of the Product register. These changes are highlighted in color. (The Product register should really be 65 bits to hold the carry out of the adder, but it's shown here as 64 bits to highlight the evolution from Figure 3.3.)

### Division

The reciprocal operation of multiply is divide, an operation that is even less frequent and even more quirky. It even offers the opportunity to perform a mathematically invalid operation: dividing by 0.

Let's start with an example of long division using decimal numbers to recall the names of the operands and the grammar school division algorithm. For reasons similar to those in the previous section, we limit the decimal digits to just 0 or 1. The example is dividing 1,001,010<sub>ten</sub> by 1000<sub>ten</sub>:

$\begin{array}{ccc} 1001_{ten} & \text{Quotient} \\ \text{Divisor } 1000_{ten} & 1001010_{ten} & \text{Dividend} \\ \hline 100 \\ 101 \\ 1010 \\ \hline -1000 \\ \hline 10_{ten} & \text{Remainder} \end{array}$

Divide's two operands, called the **dividend** and **divisor**, and the result, called the **quotient**, are accompanied by a second result, called the **remainder**. Here is another way to express the relationship between the components:

$Dividend = Quotient \times Divisor + Remainder$

#### A Division Algorithm and Hardware

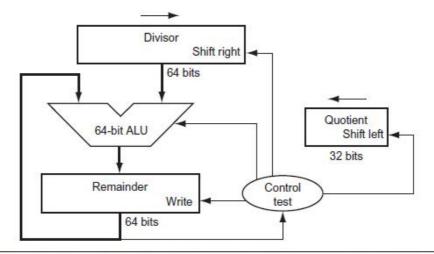

Figure 3.8 shows hardware to mimic our grammar school algorithm. We start with the 32-bit Quotient register set to 0. Each iteration of the algorithm needs to move the divisor to the right one digit, so we start with the divisor placed in the left half of the 64-bit Divisor register and shift it right 1 bit each step to align it with the dividend. The Remainder register is initialized with the dividend.

FIGURE 3.8 First version of the division hardware. The Divisor register, ALU, and Remainder register are all 64 bits wide, with only the Quotient register being 32 bits. The 32-bit divisor starts in the left half of the Divisor register and is shifted right 1 bit each iteration. The remainder is initialized with the dividend. Control decides when to shift the Divisor and Quotient registers and when to write the new value into the Remainder register.

Figure 3.9 shows three steps of the first division algorithm. Unlike a human, the computer isn't smart enough to know in advance whether the divisor is smaller than the dividend. It must first subtract the divisor in step 1; remember that this is how we performed the comparison in the set on less than instruction. If the result is positive, the divisor was smaller or equal to the dividend, so we generate a 1 in the quotient (step 2a). If the result is negative, the next step is to restore the original value by adding the divisor back to the remainder and generate a 0 in the quotient (step 2b). The divisor is shifted right and then we iterate again. The remainder and quotient will be found in their namesake registers after the iterations are complete.

| Iteration | Step                                                       | Quotient | Divisor   | Remainder  |

|-----------|------------------------------------------------------------|----------|-----------|------------|

| 0         | Initial values                                             | 0000     | 0010 0000 | 0000 0111  |

|           | 1: Rem = Rem - Div                                         | 0000     | 0010 0000 | ()110 0111 |

| 1         | 2b: Rem $< 0 \implies +$ Div, sll Q, Q0 = 0                | 0000     | 0010 0000 | 0000 0111  |

|           | 3: Shift Div right                                         | 0000     | 0001 0000 | 0000 0111  |

|           | 1: Rem = Rem - Div                                         | 0000     | 0001 0000 | ()111 0111 |

| 2         | 2b: Rem $< 0 \implies +\text{Div}, \text{ sll } Q, Q0 = 0$ | 0000     | 0001 0000 | 0000 0111  |

|           | 3: Shift Div right                                         | 0000     | 0000 1000 | 0000 0111  |

|           | 1: Rem = Rem - Div                                         | 0000     | 0000 1000 | @111 1111  |

| 3         | 2b: Rem < 0 $\implies$ +Div, sll Q, Q0 = 0                 | 0000     | 0000 1000 | 0000 0111  |

| ~         | 3: Shift Div right                                         | 0000     | 0000 0100 | 0000 0111  |

|           | 1: Rem = Rem - Div                                         | 0000     | 0000 0100 | 0000 0011  |

| 4         | 2a: Rem $\ge 0 \implies$ sll Q, Q0 = 1                     | 0001     | 0000 0100 | 0000 0011  |

|           | 3: Shift Div right                                         | 0001     | 0000 0010 | 0000 0011  |

|           | 1: Rem = Rem - Div                                         | 0001     | 0000 0010 | 0000 0001  |

| 5         | 2a: Rem $\ge 0 \implies$ sll Q, Q0 = 1                     | 0011     | 0000 0010 | 0000 0001  |

|           | 3: Shift Div right                                         | 0011     | 0000 0001 | 0000 0001  |

FIGURE 3.10 Division example using the algorithm in Figure 3.9. The bit examined to determine the next step is circled in color.

# **Floating Point**

Going beyond signed and unsigned integers, programming languages support numbers with fractions, which are called *reals* in mathematics. Here are some examples of reals:

3.14159265... ten (pi)

2.71828... ten (e)

$0.00000001_{ton}$  or  $1.0_{ton} \times 10^{-9}$  (seconds in a nanosecond)

3,155,760,000\_{ten} or 3.15576\_{ten}  $\times 10^9$  (seconds in a typical century)

Notice that in the last case, the number didn't represent a small fraction, but it was bigger than we could represent with a 32-bit signed integer. The alternative notation for the last two numbers is called **scientific notation**, which has a single digit to the left of the decimal point. A number in scientific notation that has no leading 0s is called a **normalized** number, which is the usual way to write it. For example,  $1.0_{ten} \times 10^{-9}$  is in normalized scientific notation, but  $0.1_{ten} \times 10^{-8}$  and  $10.0_{ten} \times 10^{-10}$  are not.

Just as we can show decimal numbers in scientific notation, we can also show binary numbers in scientific notation:

$$1.0_{two} \times 2^{-1}$$

### Floating-Point Representation

A designer of a floating-point representation must find a compromise between the size of the **fraction** and the size of the **exponent**, because a fixed word size means you must take a bit from one to add a bit to the other. This tradeoff is between precision and range: increasing the size of the fraction enhances the precision of the fraction, while increasing the size of the exponent increases the range of numbers that can be represented. As our design guideline from Chapter 2 reminds us, good design demands good compromise.

Floating-point numbers are usually a multiple of the size of a word. The representation of a MIPS floating-point number is shown below, where *s* is the sign of the floating-point number (1 meaning negative), *exponent* is the value of the 8-bit exponent field (including the sign of the exponent), and *fraction* is the 23-bit number. As we recall from Chapter 2, this representation is *sign and magnitude*, since the sign is a separate bit from the rest of the number.

fraction The value, generally between 0 and 1, placed in the fraction field. The fraction is also called the *mantissa*.

exponent In the numerical representation system of floating-point arithmetic, the value that is placed in the exponent field.

| 31    | 30 | 29 | 28 | 27   | 26   | 25 | 24 | 23 | 22 | 21 | 20 | <b>1</b> 9 | 18 | 17 | 16 | 15 | 14 | 13  | 12    | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----|----|----|------|------|----|----|----|----|----|----|------------|----|----|----|----|----|-----|-------|----|----|---|---|---|---|---|---|---|---|---|---|

| s     |    |    |    | expo | nent |    |    |    |    |    |    |            |    |    |    |    |    | fra | actio | n  |    |   |   |   |   |   |   |   |   |   |   |

| 1 bit |    |    |    | 81   | its  |    |    |    |    |    |    |            |    |    |    |    |    | 23  | 3 bit | s  |    |   |   |   |   |   |   |   |   |   |   |

In general, floating-point numbers are of the form

$$(-1)^{s} \times F \times 2^{E}$$

F involves the value in the fraction field and E involves the value in the exponent field; the exact relationship to these fields will be spelled out soon. (We will shortly see that MIPS does something slightly more sophisticated.)

| Single p | precision | Double p | precision | Object represented      |

|----------|-----------|----------|-----------|-------------------------|

| Exponent | Fraction  | Exponent | Fraction  |                         |

| 0        | 0         | 0        | 0         | 0                       |

| 0        | Nonzero   | 0        | Nonzero   | ± denormalized number   |

| 1-254    | Anything  | 1-2046   | Anything  | ± floating-point number |

| 255      | 0         | 2047     | 0         | ± infinity              |

| 255      | Nonzero   | 2047     | Nonzero   | NaN (Not a Number)      |

FIGURE 3.13 EEE 754 encoding of floating-point numbers. A separate sign bit determines the sign. Denormalized numbers are described in the *Elaboration* on page 222. This information is also found in Column 4 of the MIPS Reference Data Card at the front of this book.

Thus 00  $\dots$  00<sub>two</sub> represents 0; the representation of the rest of the numbers uses the form from before with the hidden 1 added:

$(-1)^{\rm S} \times (1 + {\rm Fraction}) \times 2^{\rm E}$

where the bits of the fraction represent a number between 0 and 1 and E specifies the value in the exponent field, to be given in detail shortly. If we number the bits of the fraction from *left to right* s1, s2, s3, ..., then the value is

$(-1)^{s} \times (1 + (s1 \times 2^{-1}) + (s2 \times 2^{-2}) + (s3 \times 2^{-3}) + (s4 \times 2^{-4}) + ...) \times 2^{E}$

| 31 | 30 | 29  | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21             | 20  | 10               | 18   | 17          | 16  | 15  | 14  | 13 | 12  | 11  | 10   | 9              | 8     | 7   | 6    | 5    | 4   | 3    | 2    | 1   | 0   |

|----|----|-----|----|----|----|----|----|----|----|----------------|-----|------------------|------|-------------|-----|-----|-----|----|-----|-----|------|----------------|-------|-----|------|------|-----|------|------|-----|-----|

| 1  | 1  | . 0 |    | 0  | 0  | 0  | 0  | 1  | 0  |                |     |                  |      | 0           |     |     |     |    |     |     |      |                | 10000 | 0   | -    | 0    | 0   | 100  |      |     | 1.0 |

|    |    |     |    | -  |    |    | 12 |    |    |                |     |                  |      | exp         |     |     |     |    |     |     |      |                |       | une | 2112 | acti | on  | nei  | acc  | лц  | аш  |

| AP | VS | SW  | EF | 8  |    |    | 1  |    | 2- | <sup>2</sup> = | 1/4 | <del>1</del> , o | r 0. | 25.         | Usi | ing | the | ba | sic | equ | atio | on,            |       |     |      |      |     |      |      |     |     |

| AP | NS | SW  | Eł | 8  |    |    |    |    |    |                |     |                  |      | 25.<br>tion |     | -   |     |    |     |     |      |                |       | 1 - | F 0. | .25) | ) × | 2(12 | 9-12 | 27) |     |

| A  | NS | SW  | E  | 5  |    |    |    |    |    |                |     |                  |      |             |     | -   |     |    |     | =   |      | $(1)^1 \times$ | × (   | 5 × |      |      | ) × | 2(12 | 9-12 | 27) |     |

### **Floating-Point Addition**

Let's add numbers in scientific notation by hand to illustrate the problems in floating-point addition:  $9.999_{ten} \times 10^1 + 1.610_{ten} \times 10^{-1}$ . Assume that we can store only four decimal digits of the significand and two decimal digits of the exponent.

Step 1. To be able to add these numbers properly, we must align the decimal point of the number that has the smaller exponent. Hence, we need a form of the smaller number,  $1.610_{ten} \times 10^{-1}$ , that matches the larger exponent. We obtain this by observing that there are multiple representations of an unnormalized floating-point number in scientific notation:

$$1.610_{ten} \times 10^{-1} = 0.1610_{ten} \times 10^{0} = 0.01610_{ten} \times 10^{1}$$

The number on the right is the version we desire, since its exponent matches the exponent of the larger number,  $9.999_{ten} \times 10^1$ . Thus, the first step shifts the significand of the smaller number to the right until its corrected exponent matches that of the larger number. But we can represent only four decimal digits so, after shifting, the number is really

$$0.016 \times 10^{1}$$

Step 2. Next comes the addition of the significands:

$$+ \frac{9.999_{ten}}{10.016_{ten}}$$

The sum is  $10.015_{ten} \times 10^1$ .

Step 3. This sum is not in normalized scientific notation, so we need to adjust it:

$$10.015_{tm} \times 10^1 = 1.0015_{tm} \times 10^2$$

Thus, after the addition we may have to shift the sum to put it into normalized form, adjusting the exponent appropriately. This example shows shifting to the right, but if one number were positive and the other were negative, it would be possible for the sum to have many leading 0s, requiring left shifts. Whenever the exponent is increased or decreased, we must check for overflow or underflow—that is, we must make sure that the exponent still fits in its field.

Step 4. Since we assumed that the significand can be only four digits long (excluding the sign), we must round the number. In our grammar school algorithm, the rules truncate the number if the digit to the right of the desired point is between 0 and 4 and add 1 to the digit if the number to the right is between 5 and 9. The number

$$1.0015_{ten} \times 10^{2}$$

### Floating-Point Multiplication

Now that we have explained floating-point addition, let's try floating-point multiplication. We start by multiplying decimal numbers in scientific notation by hand:  $1.110_{\text{ten}} \times 10^{10} \times 9.200_{\text{ten}} \times 10^{-5}$ . Assume that we can store only four digits of the significand and two digits of the exponent.

Step 1. Unlike addition, we calculate the exponent of the product by simply adding the exponents of the operands together:

New exponent = 10 + (-5) = 5

Let's do this with the biased exponents as well to make sure we obtain the same result: 10 + 127 = 137, and -5 + 127 = 122, so

New exponent = 137 + 122 = 259

This result is too large for the 8-bit exponent field, so something is amiss! The problem is with the bias because we are adding the biases as well as the exponents:

New exponent =  $(10 + 127) + (-5 + 127) = (5 + 2 \times 127) = 259$

Accordingly, to get the correct biased sum when we add biased numbers, we must subtract the bias from the sum:

New exponent = 137 + 122 - 127 = 259 - 127 = 132 = (5 + 127)

and 5 is indeed the exponent we calculated initially.

Step 2. Next comes the multiplication of the significands:

$$\times \underbrace{\begin{array}{c} 1.110_{\text{ten}} \\ 9.200_{\text{ten}} \\ 0000 \\ 0000 \\ 2220 \\ 9990 \\ 10212000_{\text{ten}} \end{array}}$$

There are three digits to the right of the decimal point for each operand, so the decimal point is placed six digits from the right in the product significand:

Assuming that we can keep only three digits to the right of the decimal point, the product is  $10.212 \times 10^5$ .

Step 3. This product is unnormalized, so we need to normalize it:

$10.212_{ten} \times 10^5 = 1.0212_{ten} \times 10^6$

Thus, after the multiplication, the product can be shifted right one digit to put it in normalized form, adding 1 to the exponent. At this point, we can check for overflow and underflow. Underflow may occur if both operands are small—that is, if both have large negative exponents.

Step 4. We assumed that the significand is only four digits long (excluding the sign), so we must round the number. The number

$$1.0212_{ten} \times 10^{6}$$

is rounded to four digits in the significand to

$$1.021_{tep} \times 10^{6}$$

Step 5. The sign of the product depends on the signs of the original operands. If they are both the same, the sign is positive; otherwise, it's negative. Hence, the product is

$$+1.021_{ten} \times 10^{6}$$

The sign of the sum in the addition algorithm was determined by addition of the significands, but in multiplication, the sign of the product is determined by the signs of the operands.

#### Parallelism and Computer Arithmetic: Subword Parallelism

Since every desktop microprocessor by definition has its own graphical displays, as transistor budgets increased it was inevitable that support would be added for graphics operations.

Many graphics systems originally used 8 bits to represent each of the three primary colors plus 8 bits for a location of a pixel. The addition of speakers and microphones for teleconferencing and video games suggested support of sound as well. Audio samples need more than 8 bits of precision, but 16 bits are sufficient.

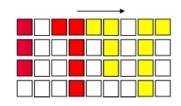

Every microprocessor has special support so that bytes and halfwords take up less space when stored in memory (see Section 2.9), but due to the infrequency of arithmetic operations on these data sizes in typical integer programs, there was little support beyond data transfers. Architects recognized that many graphics and audio applications would perform the same operation on vectors of this data. By partitioning the carry chains within a 128-bit adder, a processor could use **parallelism** to perform simultaneous operations on short vectors of sixteen 8-bit operands, eight 16-bit operands, four 32-bit operands, or two 64-bit operands. The cost of such partitioned adders was small.

Given that the parallelism occurs within a wide word, the extensions are classified as *subword parallelism*. It is also classified under the more general name of *data level parallelism*. They have been also called vector or SIMD, for single instruction, multiple data (see Section 6.6). The rising popularity of multimedia

| Data transfer               | Arithmetic                                 | Logical/Compare                     |

|-----------------------------|--------------------------------------------|-------------------------------------|

| VLDR.F32                    | VADD.F32, VADD{L,W}{S8,U8,S16,U16,S32,U32} | VAND.64, VAND.128                   |

| VSTR.F32                    | VSUB.F32, VSUB{L,W}{S8,U8,S16,U16,S32,U32} | VORR.64, VORR.128                   |

| VLD{1,2,3.4}.{I8,I16,I32}   | VMUL.F32, VMULL{S8,U8,S16,U16,S32,U32}     | VEOR.64, VEOR.128                   |

| VST{1,2,3.4}.{I8,I16,I32}   | VMLA.F32, VMLAL{S8,U8,S16,U16,S32,U32}     | VBIC.64, VBIC.128                   |

| VMOV.{I8,I16,I32,F32}, #imm | VMLS.F32, VMLSL{S8,U8,S16,U16,S32,U32}     | VORN.64, VORN.128                   |

| VMVN.{18,116,132,F32}, #imm | VMAX.{S8,U8,S16,U16,S32,U32,F32}           | VCEQ.{I8,I16,I32,F32}               |

| VMOV.{I64,I128}             | VMIN.{\$8,U8,\$16,U16,\$32,U32,F32}        | VCGE.{S8,U8,S16,U16,S32,U32,F32}    |

| VMVN.{I64,I128}             | VABS.{S8,S16,S32,F32}                      | VCGT.{S8,U8,S16,U16,S32,U32,F32}    |

|                             | VNEG.(S8,S16,S32,F32)                      | VCLE.{\$8,U8,\$16,U16,\$32,U32,F32} |

|                             | VSHL.{\$8,U8,\$16,U16,\$32,\$64,U64}       | VCLT.(\$8,U8,\$16,U16,\$32,U32,F32} |

|                             | VSHR.{S8,U8,S16,U16,S32,S64,U64}           | VTST.(18,116,132)                   |

FIGURE 3.19 Summary of ARM NEON instructions for subword parallelism. We use the curly brackets {} to show optional variations of the basic operations: {S8,U8,8} stand for signed and unsigned 8-bit integers or 8-bit data where type doesn't matter, of which 16 fit in a 128-bit register; {S16,U16,16} stand for signed and unsigned 16-bit integers or 16-bit type-less data, of which 8 fit in a 128-bit register; {S32,U32,32} stand for signed and unsigned 32-bit integers or 32-bit type-less data, of which 4 fit in a 128-bit register; {S64,U64,64} stand for signed and unsigned 64-bit integers or type-less data, of which 2 fit in a 128-bit register; {S64,U64,64} stand for signed and unsigned 64-bit integers or type-less data, of which 2 fit in a 128-bit register; {S72} stand for signed and unsigned 32-bit floating point numbers, of which 4 fit in a 128-bit register. Vector Load reads one n-element structure from memory into 1, 2, 3, or 4 NEON registers. It loads a single n-element structure to one lane (See Section 6.6), and elements of the register that are not loaded are unchanged. Vector Store writes one n-element structure into memory from 1, 2, 3, or 4 NEON registers.

# UNIT III PROCESSOR AND CONTROL UNIT

# **Basic MIPS implementation**

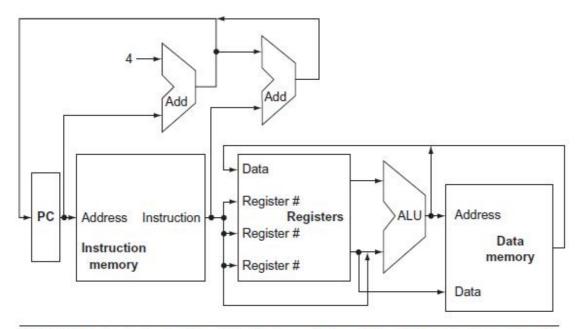

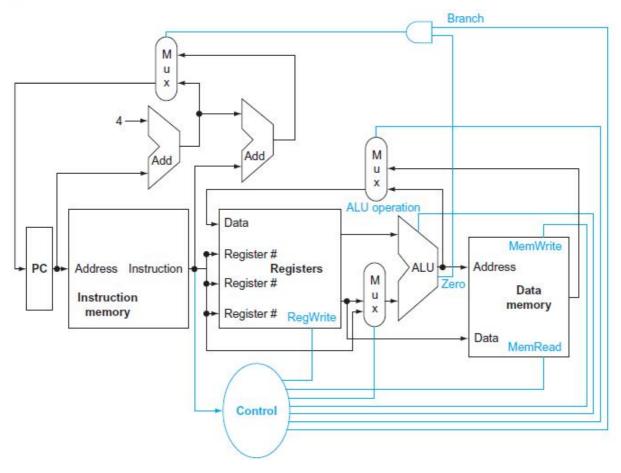

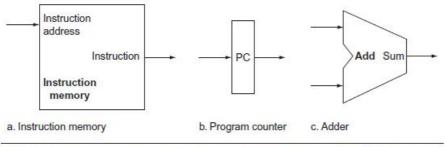

### **A Basic MIPS Implementation**

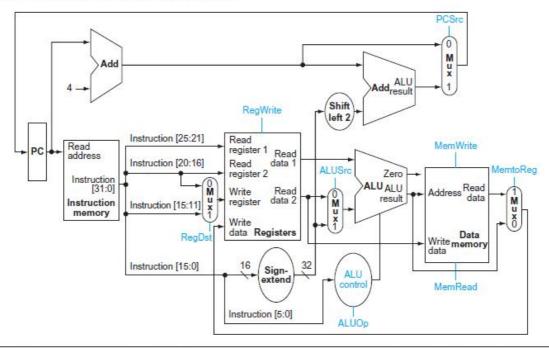

We will be examining an implementation that includes a subset of the core MIPS instruction set:

- The memory-reference instructions load word (1w) and store word (sw)

- The arithmetic-logical instructions add, sub, AND, OR, and slt

- The instructions branch equal (beq) and jump (j), which we add last

This subset does not include all the integer instructions (for example, shift, multiply, and divide are missing), nor does it include any floating-point instructions.

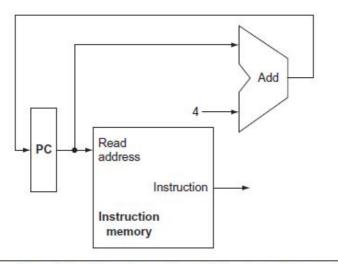

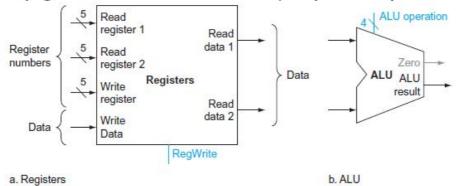

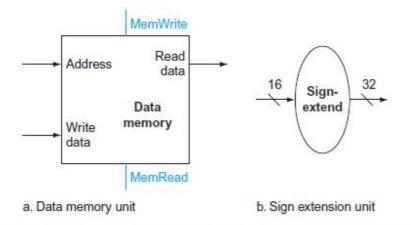

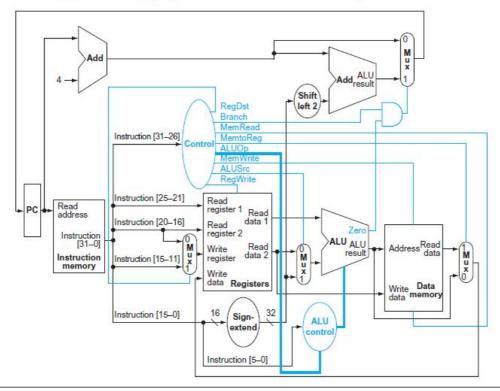

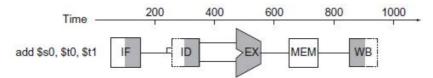

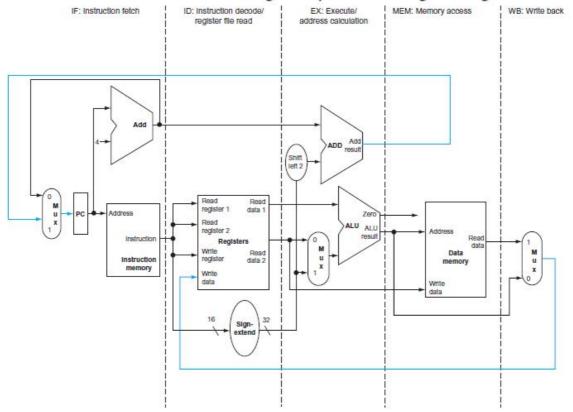

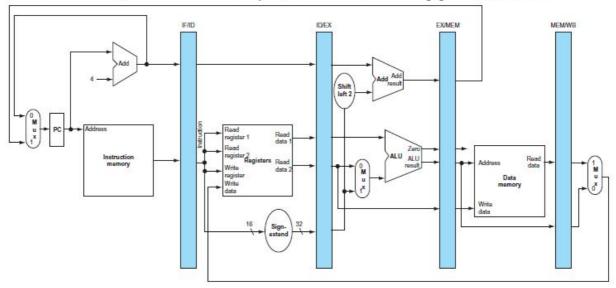

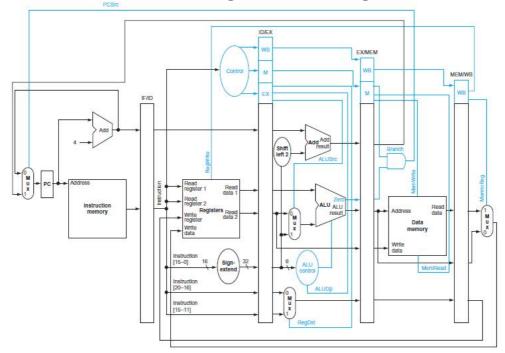

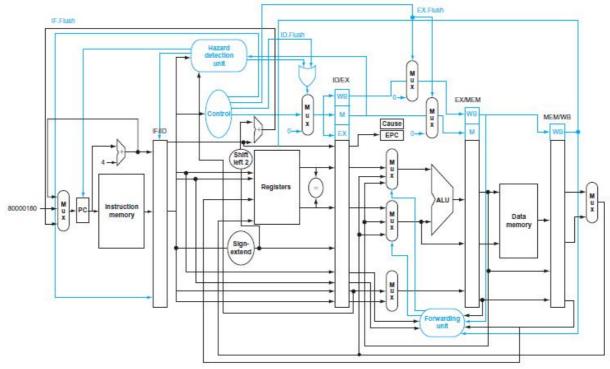

#### An Overview of the Implementation